Distinguish between MOS tube LDO principle, and how to prevent reverse current?

LDO Low Dropout Linear Regulators, traditional linear regulators have a dropout of up to 2V, but LDOs have only a few hundred mV.

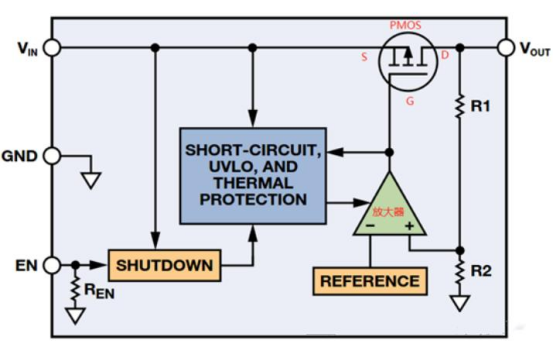

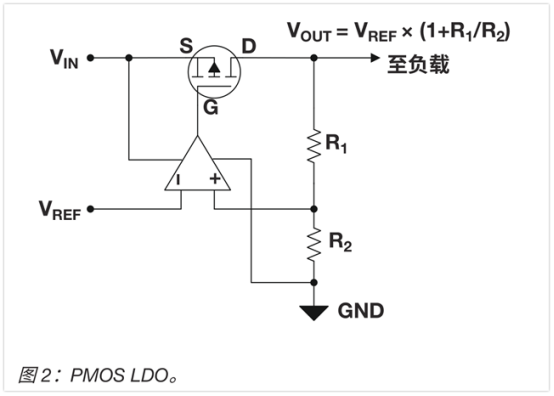

LDO belongs to a negative feedback system: when Vout increases, the voltage on R2 increases, the amplifier output voltage increases, the PMOS VGS voltage decreases, and then the output current decreases and the output voltage decreases.

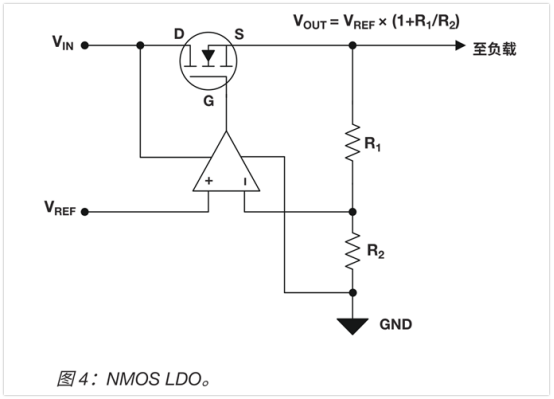

Let's compare the operation of NMOS and PMOS in an LDO.

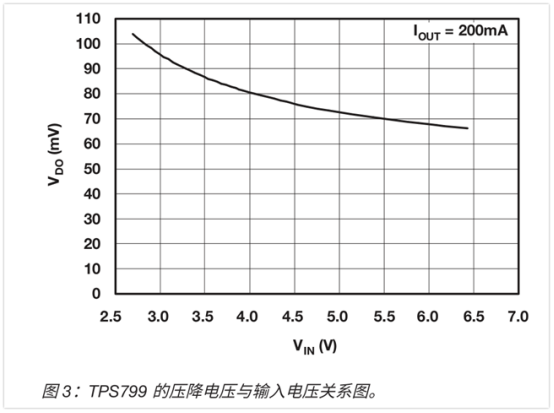

The PMOS architecture of the LDO has a lower voltage drop at a higher output voltage.

In this circuit, the feedback loop controls the drain-source resistor RDS to regulate the desired output voltage. As VIN approaches Vout, the error amplifier negatively increases the drive gate-source voltage Vgs to reduce RDS and maintain a regulated state.

However, there is a situation where the error amplifier output will reach a saturated state at the ground terminal at some specific points, and will not be able to drive the Vgs to increase further in the negative direction.

In other words, as the input voltage increases, Vgs will increase negatively, and then the dropout voltage will decrease as the input voltage increases.

In an LDO with NMOS architecture, the feedback loop still controls Rds, but as the input voltage approaches the output voltage, the error amplifier increases VGS and thus reduces RDS to maintain a regulated state.

Similarly, at a certain point, VGS can no longer be increased and the output of the error amplifier saturates at the supply voltage VIN.

At this point, RDS is minimized and multiplied by the output current IOUT, the dropout voltage.

However, the error amplifier output saturates at VIN, and as VIN approaches VOUT (nom), VGS decreases, which prevents ultra-low dropout.

Typically NMOS LDOs use an auxiliary voltage rail, which is this bias voltage. It allows the LDO to keep Vgs high and reach ultra-low dropout at low output voltages. Sometimes the auxiliary voltage rail is not provided, but it can also reach low dropout at lower output voltages, which can be replaced by an internal charge pump.

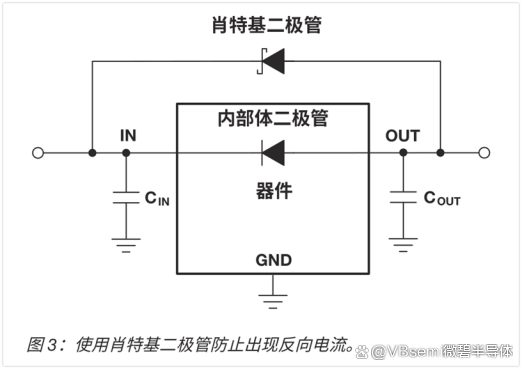

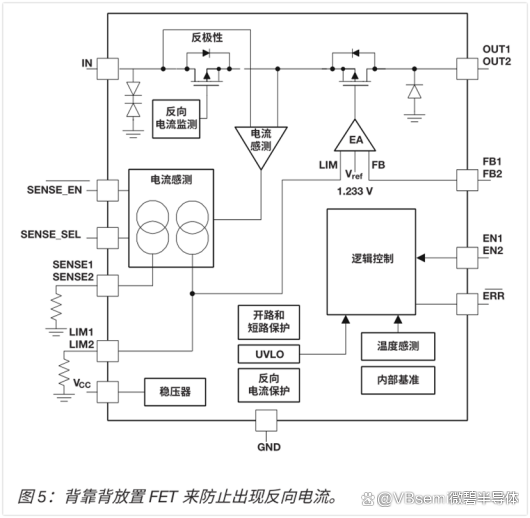

Here is a question, what if there is reverse current?

The original direction of current flow from the input voltage to the output voltage, but from the output voltage to the input voltage, this current often passes through the body diode of the LDO, will not flow through the normal conductive channel, it may lead to increased device temperature, electromigration or latch-up effect, triggering damage to the device.

The following 3 methods can be taken to prevent this.

Use Schottky diodes

2. Use a diode before the LDO

3. Add an additional FET

Above part of the picture and information from the network

Above part of the picture and information from the network

*To request free samples, please complete and submit the following information.

Our team will review your application within 24 hours and arrange shipment upon approval. Thank you!