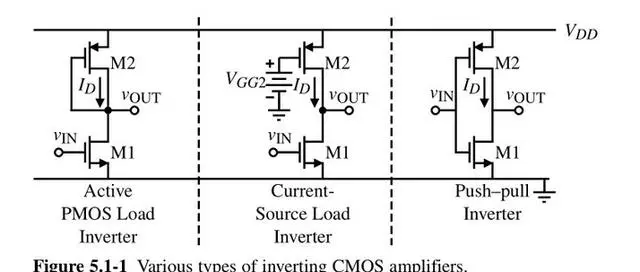

In the early days, only NMOS was used to implement logic functions due to technological limitations. Nowadays, using NMOS+PMOS is because the area occupied by MOSFETs is much smaller than that of resistors, and they have higher gain.

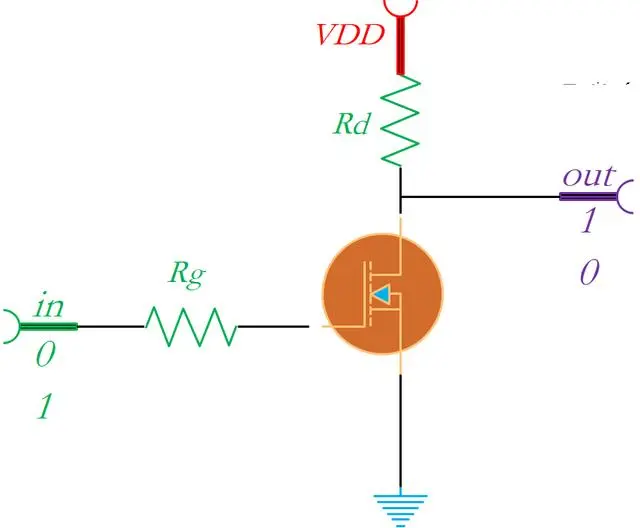

For example, consider the typical inverter circuit below:

When the input is high, a large current flows through the conducting NMOS transistor, requiring a series resistor, Rd, for current limiting. However, this already results in significant power consumption.

For applications requiring extremely low leakage current and low-power supplies, it's preferable to use MOSFETs to implement basic logic gates.

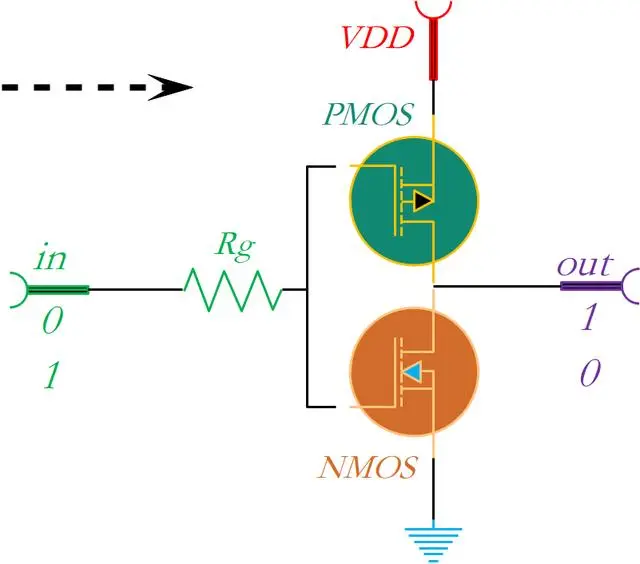

Therefore, in the above circuit, we choose to replace the resistor with a PMOS transistor, forming a complementary MOS inverter, namely CMOS inverter.

When the input is high, the lower NMOS transistor conducts, with a conductance in the milliohm range, while the upper PMOS transistor is cut off, effectively creating a milliohm resistance. The output of the inverter is low, with output voltage Vout ≈ 0, and the current passing through both ends is close to 0, significantly reducing circuit power consumption.

When the input is low, the lower NMOS transistor is cut off, and the upper PMOS transistor conducts. The output of the inverter is high, with output voltage Vout ≈ VDD, and the current consumption depends on the receiving end of the out signal. The CMOS inverter approaches an ideal logic unit, with output voltage close to 0 or VDD.

Inverters have several important parameters when dealing with high-frequency signals. If the inverter's transition is not fast enough, it can lead to distortion when processing high-frequency signals.

Static current: Current directly determines power consumption. In single NMOS/PMOS usage, one of the logic states always conducts, whereas CMOS only has a brief high current during transition, with no significant current during steady-state operation.

VTC performance: Including gain speed, threshold voltage, noise immunity, transition region slope, etc.

Component size: In integrated circuits, resistors take up more space. Therefore, considering all aspects of performance, CMOS inverters are the preferred choice.

In summary, when using only one MOSFET, a pull-up resistor is required, but this leads to a larger structure and higher static power consumption. However, by pairing NMOS and PMOS on a substrate and using CMOS, with PMOS providing pull-up and NMOS pull-down, the inverter can output high-quality high and low logic levels in static operation without relying on pull-up/pull-down resistors, and achieves very low static power consumption.

*To request free samples, please complete and submit the following information.

Our team will review your application within 24 hours and arrange shipment upon approval. Thank you!